XNOR gate - XNOR gate

| Inngang | Produksjon | |

|---|---|---|

| EN | B | A XNOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Den XNOR port (noen ganger enor , EXNOR eller NXOR og uttalt som eksklusive NOR ) er en digital logisk portkrets hvis funksjon er det logiske komplement av den eksklusive ELLER ( XELLER ) port. Det tilsvarer den logiske forbindelsen ( ) fra matematisk logikk , også kjent som materialet biconditional. To-input-versjonen implementerer logisk likhet og oppfører seg i henhold til sannhetstabellen til høyre, og derfor kalles porten noen ganger en "ekvivalensport". En høy utgang (1) oppstår hvis begge inngangene til porten er de samme. Hvis en men ikke begge inngangene er høye (1), resulterer en lav utgang (0).

Den algebraiske notasjonen som brukes for å representere XNOR -operasjonen er . Den algebraiske uttrykk og begge representerer XNOR port med inngangene A og B .

Symboler

Det er to symboler for XNOR -porter : ett med særpreget form og ett med rektangulær form og etikett. Begge symbolene for XNOR -porten er XOR -porten med en ekstra inversjonsboble.

Maskinvarebeskrivelse

XNOR -porter er representert i de fleste TTL- og CMOS IC -familier. Standard 4000-serien CMOS IC er 4077, og TTL IC er 74266 (selv om det er en åpen samlerimplementering ). Begge inkluderer fire uavhengige, to-inngangs, XNOR-porter. Den (nå foreldede) 74S135 implementerte fire to-inngangs XOR/XNOR-porter eller to tre-inngangs XNOR-porter.

Både TTL 74LS- implementeringen, 74LS266, så vel som CMOS-portene (CD4077, 74HC4077 og 74HC266 og så videre) er tilgjengelig fra de fleste halvlederprodusenter som Texas Instruments eller NXP , etc. De er vanligvis tilgjengelige i begge gjennomgående DIP og SOIC- formater (SOIC-14, SOC-14 eller TSSOP-14).

Dataark er lett tilgjengelig i de fleste datablad og leverandører.

Pinout

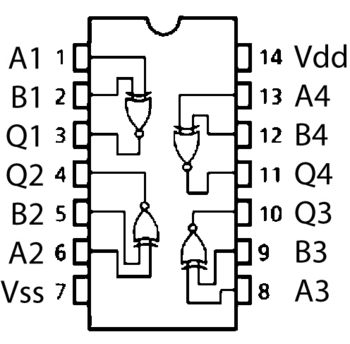

Både 4077- og 74x266 -enhetene (SN74LS266, 74HC266, 74266, etc.) har samme pinout -diagram, som følger:

Pinout-diagram over 74HC266N, 74LS266 og CD4077 quad XNOR plast in-line pakke 14-pinners pakke ( PDIP-14 ) ICer .

- Inngang A1

- Inngang B1

- Utgang Q1 (høy hvis og bare hvis A1 og B1 har samme logiske nivå)

- Utgang Q2

- Inngang B2

- Inngang A2

- V ss (GND) felles strøm og signaljordstift

- Inngang A3

- Inngang B3

- Utgang Q3

- Utgang Q4

- Inngang B4

- Inngang A4

- V dd for CMOS (V cc for TTL) positiv strømforsyning (se datablad for akseptable spenningsområder)

Alternativer

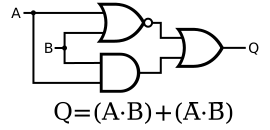

Hvis en bestemt type gate ikke er tilgjengelig, kan en krets som implementerer den samme funksjonen konstrueres fra andre tilgjengelige porter. En krets som implementerer en XNOR -funksjon kan enkelt konstrueres fra en XOR -port etterfulgt av en NOT -port. Hvis vi vurderer uttrykket , kan vi konstruere en XNOR -portkrets direkte ved å bruke AND, OR og NOT portene. Denne tilnærmingen krever imidlertid fem porter av tre forskjellige slag.

Som alternativ, hvis forskjellige porter er tilgjengelige, kan vi bruke boolsk algebra for å transformere som angitt ovenfor, og bruke de Morgans lov til det siste uttrykket for å få som kan implementeres ved å bruke bare tre porter som vist til høyre.

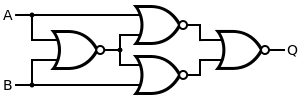

En XNOR -portkrets kan lages fra fire NOR -porter. Faktisk er både NAND- og NOR-porter såkalte "universelle porter", og enhver logisk funksjon kan konstrueres ut fra enten NAND-logikk eller NOR-logikk alene. Hvis de fire NOR -portene erstattes av NAND -porter, resulterer dette i en XOR -port, som kan konverteres til en XNOR -port ved å invertere utgangen eller en av inngangene (f.eks. Med en femte NAND -port).

| Ønsket port | NAND konstruksjon | NOR konstruksjon |

|---|---|---|

|

|

|

Et alternativt arrangement er av fem NAND-porter i en topologi som understreker konstruksjonen av funksjonen fra , og bemerker fra de Morgans lov at en NAND-port er en invertert inngang ELLER gate. En annen alternativ ordning er fem NOR-porter i en topologi som understreker konstruksjonen av funksjonen fra , og bemerker fra de Morgans lov at en NOR-port er en invertert inngang OG port.

| Ønsket port | NAND konstruksjon | NOR konstruksjon |

|---|---|---|

|

|

|

For NAND -konstruksjonene gir det nedre arrangementet fordelen med en kortere forplantningsforsinkelse (tidsforsinkelsen mellom en inngang som endres og utgangen endres). For NOR -konstruksjonene krever det øvre arrangementet færre porter.

Fra det motsatte perspektivet er det mulig å konstruere andre porter som bare bruker XNOR -porter, selv om XNOR ikke er en fullt universell logisk port . NOT og XOR -porter kan konstrueres på denne måten.

Mer enn to innganger

Selv om andre porter (OR, NOR, AND, NAND) er tilgjengelige fra produsenter med tre eller flere innganger per gate, er dette ikke strengt tatt sant med XOR- og XNOR -porter. Men å utvide konseptet med den binære logiske operasjonen til tre innganger, SN74S135 med to delte "C" og fire uavhengige "A" og "B" innganger for sine fire utganger, var en enhet som fulgte sannhetstabellen:

| Inngang | Produksjon | ||

|---|---|---|---|

| EN | B | C | Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Dette er effektivt Y = NOT ((A XOR B) XOR C). En annen måte å tolke dette på er at utgangen er sann hvis et jevnt antall innganger er sant. Den implementerer ikke en logisk "ekvivalens" -funksjon, i motsetning til to-inngangs XNOR-porter.

I tillegg ser det ut til at XOR -funksjonen fungerer som en paritetsfunksjon eller Mod2 for summen av alle innganger. Legg merke til hvordan * y * er lik 1 hvis summen av alle innganger er jevn, noe som betyr at y = 0 hvis summen av alle innganger er oddetall. Vi kan konkludere med dette at x XOR y XOR z = er partall (x+y+z).

Se også

- OG port

- ELLER port

- IKKE port

- NAND gate

- NOR gate

- XOR -port

- Kronecker delta -funksjon

- Logisk tobetinget

- Hvis og bare hvis

Referanser

- ^ "Exclusive-NOR Gate Tutorial" . Hentet 6. mai 2018 .

- ^ "XNOR Logic Gates" . Besøkt 6. mai 2018 .